超大规模集成电路设计方法学导论

引言:从想法到硅片

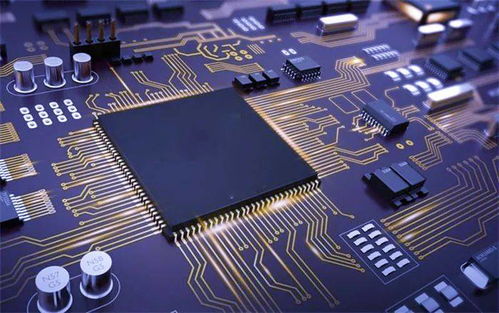

超大规模集成电路(VLSI)设计是现代信息技术的基石,它涉及将数以亿计的晶体管集成到单一芯片上,实现复杂的功能。随着半导体工艺的不断演进,晶体管尺寸持续缩小,芯片复杂度呈指数级增长,这使得传统的设计方法难以应对。因此,一套系统化、层次化、自动化的设计方法学应运而生,旨在高效、可靠地将抽象的概念转化为物理的硅片。

核心设计流程:自顶向下与层次化

VLSI设计通常遵循“自顶向下”的设计哲学,这是一个从抽象到具体、从系统级到物理级的逐层细化过程。

- 系统设计与架构规划:这是设计的起点。设计者需要明确芯片的功能、性能指标(如速度、功耗、面积)和外部接口。在此阶段,通常使用高级建模语言(如SystemC、Matlab)进行算法验证和架构探索,以确定最优的硬件-软件划分和系统级互连方案。

- 寄存器传输级设计:在架构确定后,设计进入RTL级。设计者使用硬件描述语言(如Verilog或VHDL)将功能描述为寄存器之间的数据传输和逻辑操作。此阶段产生的代码是后续所有自动化和验证的基础。功能仿真是此阶段的关键,以确保逻辑行为的正确性。

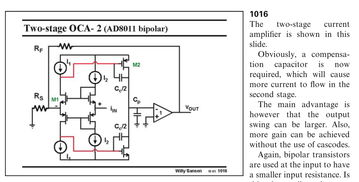

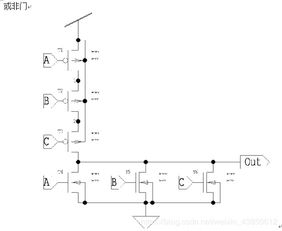

- 逻辑综合:这是方法学自动化的核心环节之一。综合工具将RTL代码、目标工艺库(包含标准单元的特性)以及设计约束(如时序、面积)作为输入,自动生成门级网表。这个网表是由基本逻辑门(如与门、或门、触发器等)构成的电路连接图。

- 物理设计:将门级网表转换为芯片的几何版图。这个过程主要包括:

- 布局:确定每个标准单元在芯片平面上的位置。

- 布线:根据电路的连接关系,在单元之间布设金属连线。

- 时序收敛与优化:确保信号在布线后仍能满足时序要求,这是一个需要反复迭代的挑战性工作。

- 设计规则检查:确保版图符合芯片制造工艺的物理和电气规则。

- 验证与签核:在设计流程的每个阶段,验证都至关重要。这包括功能验证、形式验证、静态时序分析、功耗分析以及物理验证等。只有通过所有签核检查,设计才能交付给晶圆厂进行流片制造。

现代设计方法学的关键支撑技术

- 电子设计自动化工具:EDA工具链是VLSI设计方法学的引擎,涵盖了从仿真、综合、布局布线到验证的所有环节。工具的性能和智能化程度直接决定了设计效率和质量。

- 知识产权核复用:为了应对设计复杂性并缩短上市时间,预先设计好并经过验证的功能模块(IP核,如CPU内核、内存控制器、接口IP)被广泛复用。这要求设计方法学必须支持模块化、接口标准化和系统级集成。

- 可制造性设计:随着工艺进入深亚微米及以下节点,制造过程中的光学效应、工艺波动等对芯片性能的影响变得不可忽视。DFM技术通过在设计中预先考虑并规避这些制造缺陷,来提高芯片的良率和可靠性。

- 低功耗设计:功耗已成为与性能、面积并列的核心设计约束。方法学从系统架构、RTL编码、综合到物理设计各层级都融入了功耗管理技术,如时钟门控、电源门控、多电压域等。

未来挑战与发展趋势

面对后摩尔时代,VLSI设计方法学正经历深刻变革:

- 系统级芯片与异构集成:将计算、存储、射频、传感等不同工艺、不同功能的芯片通过先进封装(如2.5D/3D IC)集成在一起,这要求设计方法学从单芯片扩展到多芯片系统。

- 人工智能与机器学习:AI/ML技术正被用于优化EDA工具本身,例如预测布线拥塞、加速物理设计迭代、进行设计空间探索,从而提升自动化水平和设计效率。

- 安全性设计:硬件安全成为不可或缺的一环,安全考量必须“左移”,从设计伊始就融入方法学流程中。

###

超大规模集成电路设计方法学是一门融合了计算机科学、电子工程和微电子技术的综合性学科。它通过一套严谨的流程、强大的工具和不断演进的最佳实践,驾驭着日益增长的芯片复杂性。掌握这套方法学,不仅是将创新想法变为现实产品的关键,也是推动整个半导体产业持续向前发展的核心动力。对于设计者而言,理解并灵活运用这一方法学,是在这个高精尖领域立足的根本。

如若转载,请注明出处:http://www.wifi-camera-alarm.com/product/15.html

更新时间:2026-04-24 02:18:57