现代集成电路版图设计 芯片制造的蓝图与灵魂

集成电路设计是现代信息技术的基石,而其中的版图设计环节,则是连接抽象电路概念与物理硅芯片的关键桥梁。它不仅是芯片制造的“施工蓝图”,更是决定芯片性能、功耗、可靠性和成本的核心要素。

版图设计的内涵与流程

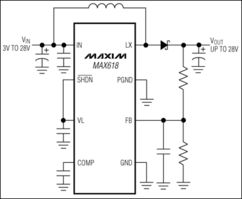

版图设计,又称物理设计,是在逻辑电路设计完成之后,将晶体管、电阻、电容等元器件以及它们之间的互连线,按照特定的设计规则,在硅片平面上转化为精确的几何图形和物理层次的过程。这个过程极其复杂,通常包括以下几个关键步骤:

- 布局:确定芯片上各个功能模块(如运算单元、存储器、接口等)的宏观位置和形状。目标是优化芯片面积、缩短关键信号路径、并考虑散热和电源分布。

- 布线:在布局确定的基础上,用金属线将各个元器件和模块按照电路连接关系实际地连接起来。这需要在多层(现今可达十几层)金属互连层中进行三维规划,解决信号完整性、串扰、时钟偏差和电源网络等难题。

- 物理验证:完成初步版图后,必须进行严格的验证,包括设计规则检查(DRC,确保图形尺寸符合晶圆厂工艺要求)、电气规则检查(ERC,确保无短路、开路等电气错误)以及版图与电路图一致性检查(LVS,确保物理实现与原始电路逻辑完全匹配)。

面临的挑战与关键技术

随着半导体工艺进入纳米尺度(如5nm、3nm),版图设计面临着前所未有的挑战:

- 工艺复杂性:先进工艺的几何尺寸逼近物理极限,设计规则极其复杂,需要考虑制造过程中的光刻、刻蚀、化学机械抛光等效应,引入了可制造性设计(DFM)等理念。

- 功耗与散热:晶体管密度激增,导致功耗密度巨大,局部“热点”问题严重。版图设计必须精心规划电源网络和散热路径,采用功耗优化策略。

- 信号完整性:导线间距极小,互连延迟已超过门延迟,成为性能瓶颈。串扰、电迁移、电压降(IR Drop)等问题对布线和电源网络设计提出了极高要求。

- 设计规模与效率:一个芯片可能包含数百亿个晶体管,完全依靠人工设计已不可能。因此,电子设计自动化(EDA)工具和智能算法(如人工智能辅助布局布线)变得至关重要。

发展趋势与未来展望

集成电路版图设计将继续向更高层次的自动化和智能化发展。一方面,EDA工具将集成更多基于机器学习和物理仿真的优化引擎,帮助设计师更高效地探索设计空间,实现性能、功耗和面积(PPA)的最佳平衡。另一方面,随着芯粒(Chiplet)和异构集成技术的兴起,版图设计的范畴从单一芯片扩展到多芯片系统,需要考虑硅中介层、先进封装中的互连与集成,进入了“系统级”版图设计的新时代。

现代集成电路版图设计是一门融合了电子工程、计算机科学、物理学和数学的精密艺术与科学。它既是芯片从构想变为现实的必经之路,也是推动摩尔定律持续前行、释放芯片创新潜力的核心驱动力。随着技术的演进,版图设计师的角色将更多地转向策略制定、约束管理和工具驾驭,以应对日益复杂的设计挑战,继续为数字世界绘制精密而强大的底层蓝图。

如若转载,请注明出处:http://www.wifi-camera-alarm.com/product/32.html

更新时间:2026-04-22 08:11:40