通道门阵列的栅格结构 集成电路设计方法学中的核心视角

在集成电路设计方法学中,通道门阵列的栅格结构是一个至关重要的概念,它深刻影响了芯片的布局、布线与整体性能。要理解其重要性,我们需要从设计方法学、物理实现和性能优化等多个维度进行审视。

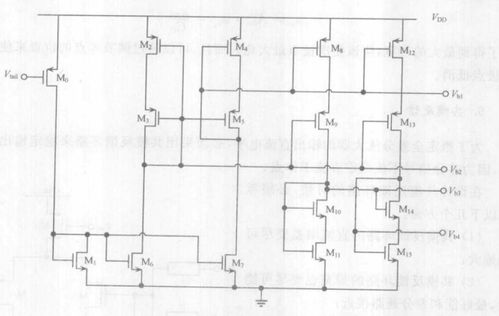

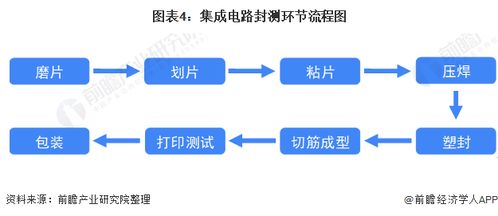

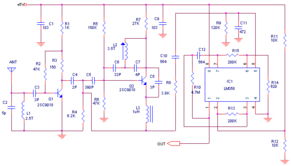

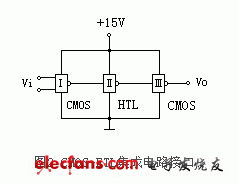

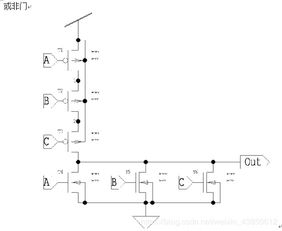

从设计方法学角度看,通道门阵列是一种半定制集成电路。其核心思想是在硅片上预先制造出由大量相同的基本逻辑单元(如与非门、或非门)和规则排列的互连通道组成的规则阵列。这里的“栅格结构”正是这种规则性的物理体现。设计师的任务不是从零开始绘制每一个晶体管,而是在这个预先定义好的“画布”上,通过有选择地连接这些基本单元和通道,来实现特定的逻辑功能。这种方法学极大地提高了设计效率,降低了设计门槛和成本,是早期ASIC设计的主流方法之一。栅格结构的规则性使得自动布局布线工具能够高效工作,这是其方法学优势的基石。

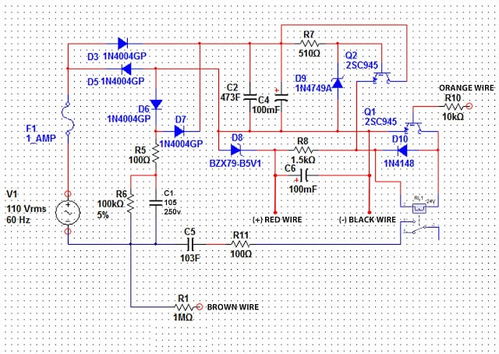

深入栅格结构的物理细节,它通常呈现为行、列交错的棋盘状图案。基本逻辑单元被放置在由垂直和水平布线通道分隔开的“岛屿”或“行”上。这些布线通道本身也是按固定宽度和间距的栅格进行规划。这种结构的优点在于可预测性和规整性。其缺点也显而易见:由于布线资源是预先分配且固定的,对于高度复杂或不规则的设计,可能会出现布线通道不足或利用率低下的问题,导致芯片面积利用率不高,性能可能不及全定制设计。

从性能与优化视角分析,栅格结构直接关系到芯片的时序、功耗和信号完整性。在通道门阵列中,信号的传输路径长度、经过的逻辑单元数量以及互连线的寄生参数(电阻、电容)都受到底层栅格结构的约束。设计师和EDA工具需要在给定的栅格框架内,通过优化单元放置和通道内的布线路径,来满足时序要求、降低串扰和功耗。栅格的密度和通道的宽度是需要权衡的关键参数:更密的栅格能提供更灵活的布线,但可能增加工艺复杂度;更宽的通道能确保布通率,但会浪费面积。

在当代技术背景下看,虽然通道门阵列在很大程度上已被更灵活的标准单元库和门海设计所取代,但其蕴含的“规整化设计”思想依然影响深远。例如,在FPGA和某些结构化ASIC中,我们依然能看到基于栅格或类似阵列架构的设计哲学。理解通道门阵列的栅格结构,有助于我们把握集成电路从规整化向高密度、高性能、异质化集成演进的设计脉络。

在集成电路设计方法学中看待通道门阵列的栅格结构,不应仅将其视为一种过时的物理布局,而应视其为一个体现了设计效率、物理约束与性能权衡的经典范式。它代表了在自动化与定制化之间寻求平衡的一种重要解决方案,其设计思想至今仍具启发意义。

如若转载,请注明出处:http://www.wifi-camera-alarm.com/product/25.html

更新时间:2026-04-06 10:44:48