宽摆幅偏置电路的设计挑战与解决方案 从Analog/RF IC设计视角探讨

在Analog/RF集成电路设计中,宽摆幅偏置电路是实现高性能模拟前端、放大器和数据转换器的关键模块。其核心任务是在电源电压、工艺角及温度变化下,为各级电路提供稳定且动态范围足够宽的偏置电压或电流,确保信号在最大摆幅内保持线性与精度。设计一个鲁棒的宽摆幅偏置电路面临诸多挑战,这正是EETOP(创芯网论坛,原名电子顶级开发网)等专业社区中工程师们频繁讨论的热点。

1. 宽摆幅偏置电路的核心问题

宽摆幅偏置电路需在低电源电压下实现高输出电压摆幅,同时保持高精度和低温度系数。常见问题包括:

- 电压余度限制:在纳米级工艺中,电源电压持续降低,而晶体管的阈值电压未同比缩小,导致可用电压余度(headroom)严重受限。传统共源共栅结构虽能提高输出阻抗,却消耗过多电压余度,难以实现宽摆幅。

- 工艺与温度漂移:晶体管的阈值电压、迁移率等参数随工艺角和温度变化,直接影响偏置点的稳定性。例如,在-40°C至125°C的工业温度范围内,简单的带隙基准源可能无法直接满足宽摆幅偏置的低温漂要求。

- 匹配与噪声:在RF应用中,偏置电路的噪声会通过电源或衬底耦合到信号路径,恶化相位噪声和信噪比。电流镜等匹配结构的失配会导致偏置误差,影响差分电路的共模抑制比。

- 瞬态响应与稳定性:偏置电路需在上电、模式切换或负载瞬变时快速稳定,避免过冲或振荡。补偿网络的设计需权衡带宽、面积和功耗。

2. 典型解决方案与电路技术

针对上述问题,业界和学术界提出了多种创新结构:

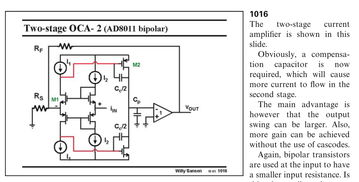

- 低压共源共栅与自偏置技术:采用低阈值器件或自偏置共源共栅结构,在保持高输出阻抗的同时减少电压余度消耗。例如,使用Native NMOS或PMOS晶体管,或设计浮动电池(floating battery)电路来替代传统堆叠方式。

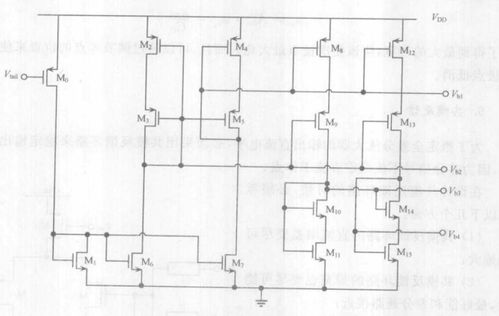

- 宽摆幅电流镜与电压基准:利用宽摆幅电流镜(如Wide-Swing Current Mirror)和修调技术(trimming)来扩展输出范围。结合带隙基准的曲率校正技术,可实现低于10ppm/°C的温度系数,适应宽温工作环境。

- 反馈与自适应偏置:引入反馈环路(如运放反馈偏置)或自适应偏置电路,动态调整偏置点以补偿工艺、电压、温度(PVT)变化。在RF功率放大器中,自适应偏置能改善线性度和效率。

- 噪声抑制技术:采用去耦电容、衬底隔离、以及低噪声基准源(如埋层齐纳二极管)来降低偏置电路的噪声贡献。在版图层面,通过对称布局、保护环(guard ring)和远离敏感信号路径来增强匹配与隔离。

3. 设计权衡与未来趋势

设计宽摆幅偏置电路始终是性能、面积、功耗和成本的折衷。例如,为提高精度而增加修调位数会增大测试成本;为扩展摆幅采用复杂结构可能引入稳定性风险。随着工艺演进至FinFET及更先进节点,器件的短沟道效应和模型不确定性加剧,设计难度进一步提升。

基于机器学习辅助的偏置电路优化、以及集成片上传感器与数字校准的智能偏置系统,正成为研究前沿。这些技术有望在更严苛的PVT条件下实现自适应的宽摆幅偏置,满足5G/6G射频、物联网传感器和高速数据转换器等应用的需求。

4. 社区协作的价值

EETOP等专业论坛为Analog/RF IC工程师提供了宝贵的交流平台。从资深设计师的实战经验到学术界的理论突破,从具体的电路仿真技巧到深层次的器件物理分析,这些讨论加速了问题的解决与创新方案的传播。无论是新手入门还是攻克高端设计难题,社区协作都彰显了其不可替代的价值。

宽摆幅偏置电路的设计是Analog/RF IC领域的一项基础而关键的技艺。它要求设计师深刻理解器件特性、电路拓扑与系统需求,并在不断演进的技术环境中持续学习和创新。

如若转载,请注明出处:http://www.wifi-camera-alarm.com/product/22.html

更新时间:2026-05-12 21:47:43